为什么你的MOS管总炸?FPGA起不来?

作为硬件工程师,你是否经历过这种“玄学”时刻:

❌ 样机上电瞬间,前级DC-DC莫名过流保护,甚至直接炸机?

❌ 电源轨电压明明到了,但FPGA/DSP就是无法加载,甚至芯片发烫锁死?

❌ 示波器抓到的波形看似正常,后端负载却概率性罢工?

如果中招了,别急着换芯片,先检查你电源设计里那个毫不起眼的参数——软启动。今天咱们从原理到底层,彻底讲透这个让无数新手“翻车”的关键指标。

第一:别把“启动”当成“软启动”

很多工程师在测试电源时,习惯把“上电”看作一个瞬间动作。但在毫秒级的时间轴下,这其实是一套复杂的组合拳。如果不搞清楚延迟和爬升的区别,你的测试报告很可能就是错的。

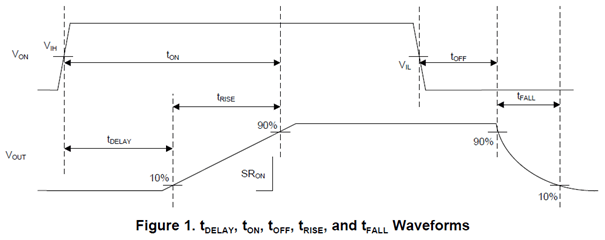

我们先看这张最经典的“标准定义图”,这里面藏着三个关键时序:

图1.1

当你拉高使能脚(EN)的那一刻,电源内部其实发生了两段截然不同的故事:

使能延迟时间:芯片的“起床气”

原文明确指出,这是从EN信号超过有效阈值(Enable Threshold)开始,到输出电压刚刚到达目标值 10% 的这段时间 。

深度解读: 在这段时间里,V_OUT 几乎是0。芯片内部正在忙着建立偏置电压、校准基准源、自检过温过流保护电路。这是芯片的“生理反应时间”,你外部加电容也改变不了它。

软启动时间:真正的“爬坡期”

这才是我们今天的主角!定义为输出电压从 10% 单调上升到 90% 所需的时间 。

为什么高手关注它? 原文特别提到一个核心概念:软启动时间与输出电压上升斜率(Slew Rate)成反比 。

实战意义: 有些负载(如FPGA)对“时间”敏感(要求多少ms内起来),而有些对“斜率”敏感(要求电压变化率不能太快)。本质上它们是一个指标的两个维度。如果你不理解这个转换关系,就很难满足高端芯片的严苛上电要求 。

这里有一个极易踩的坑:

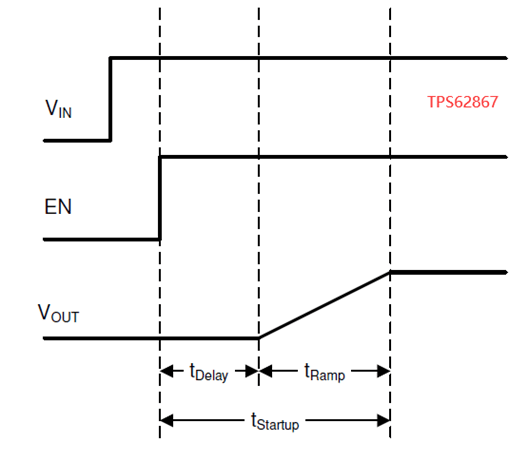

业界对于“启动参数”并没有完全统一的国标或行标 。请看下面这张图,展示了另一种常见的定义方式:

图1.2

定义差异: 有些芯片(如图1.2)将“启动时间”定义为从 EN上升沿的50% 开始,一直到 V_OUT达到50% 为止 。

这意味着,如果你拿图5.60的测试方法去测定义为图5.61的芯片,你的测试结果不仅不准,甚至可能因为测量点选取错误,导致判断产品“不合格”。所以,测量结果是否合规,必须死磕具体电源芯片的规格书,不能想当然! 。

总结一下,一个严谨的“启动时间”公式应该是这样的:

启动时间=使能延迟(死区等待)+软启动时间(斜率爬升)

图 1.3 电源电路的启动时间、使能延迟时间、软启动时间

第二:为什么要人为把启动“变慢”?

有些新手会问:“电源不是上电越快越好吗?”错错错,是你的错.....!

软启动的核心目的,是在启动瞬间控制浪涌电流和电压上升斜率 。如果没有这个“刹车”机制,物理定律会给你的电路板带来两个致命打击:

1. 抑制浪涌电流

我们先看这个经典的电容充电公式:

在电源启动的瞬间,输出电容 COUT 上的电压是0,此时它等效于一个短路状态。

如果不加软启动: 启动时间极短(dt→0),这意味着 dV/dt无穷大。此时,你需要一个巨大的瞬间电流来给电容充电。

后果很严重:

触发限流或炸机: 这个巨大的充电电流可能瞬间超过开关电源的电流限值,导致电源启动失败,甚至直接对开关管(MOSFET)造成不可逆的电流应力损伤 。

拉垮前级电源: 能量守恒定律告诉我们,输出端的巨大能量需求必须由输入端提供。瞬间的大电流会把输入电压拉低,这就像家里空调启动瞬间灯会暗一下。如果跌落太严重,前级的其他芯片可能会复位或掉电 。

解法: 软启动就是人为拉长dt,把那个尖峰电流“削平”,让它在一个可控的范围内缓慢给电容充电,大家相安无事。

2. 保证单调性

这一个点是很多做纯模拟电源的工程师容易忽略的。原文特别强调:配置合理的软启动时间,是为了让输出电压“单调上升”,绝对不能出现抖动 。

什么是单调性? 就是电压只能涨,不能跌。

为什么要单调? 像FPGA、DSP、ASIC这种复杂的数字器件,对上电时序有极高的要求。如果启动太快,环路响应过激,电压上升过程中可能会出现过冲然后回落(震荡)。

后果: 在上电复位阶段,如果电压突然抖动一下,数字逻辑可能会陷入混乱,甚至触发闩锁效应——芯片内部形成寄生可控硅导通,导致电源与地之间短路,芯片发烫、死机,甚至永久烧毁 。

所以,软启动不仅仅是保护电源本身,更是为了保护后面那些昂贵的“大脑”芯片。

第三:怎么配置软启动?

在选型和设计时,我们通常面临两种选择。这里以经典的 TI 降压芯片为例,进行一次“像素级”的深度对比:

方案 A:内部软启动

代表芯片: TPS54560

原理深挖: 这颗芯片采用的是内部数字软启动。它不是靠模拟电容充放电,而是在芯片内部集成了一个计数器 。

当EN使能且电压正常后,芯片开始数数。

它强制规定:输出电压必须在 1024个开关周期 内,从0V爬升到目标值 。

这意味着,FB引脚的参考电压是按台阶一步步“强行”抬上去的。

图 3.1 TPS54560DDA器件的软启动时间计算公式及典型值

致命局限: 既然是按“周期数”来算的,那么软启动时间 (tss) 就和开关频率 (fsw) 彻底锁死成反比关系。公式如下:

场景还原: 假设为了缩小电源体积,你把频率推高到 2.5MHz。此时,软启动时间会被强制压缩到只有 0.42ms !

后果: 你想慢都慢不下来。极短的启动时间会导致巨大的电压变化率 (dV/dt),进而引发浪涌电流报警。这就是“省了空间,丢了控制”。

方案 B:外部软启动

代表芯片: TPS54560

一眼看穿区别: 对比引脚图,TPS54561 多了一个关键的 SS/TR 引脚。这一个小小的引脚,就是新手与高手的由分水岭 。

图 3.2 TPS54560DDA与TPS54561DPRT引脚对比

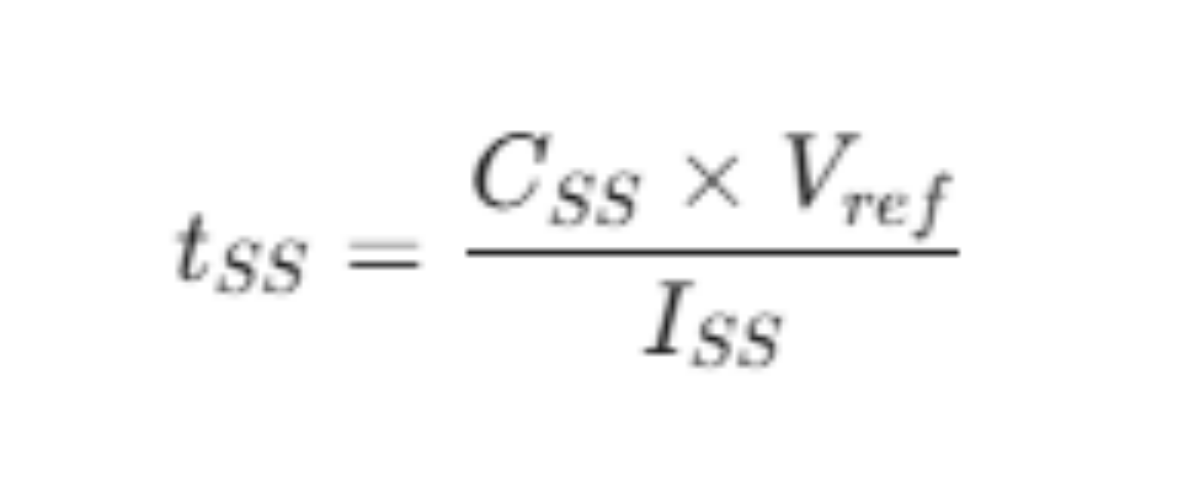

高阶玩法解析: 它的内部不再是死板的计数器,而是一个高精度的恒流源充电电路 。

恒流充电: 芯片内部有一个 1.7uA 的电流源,专门负责给外部挂的电容 Css 充电 。

电压跟踪: SS引脚上的电压 Vss 会从0V开始线性上升。芯片内部的误差放大器不仅看内部基准电压,还会盯着 Vss 看——谁小听谁的。

结果: 输出电压 Vout 会乖乖地跟着 Css 上的电压斜率爬升,直到 Vss 超过内部基准。

图 3.3 TPS54561DPRT器件软启动相关参数

绝对优势:

完全解耦: 你的启动时间 tss 只取决于你选的电容 Css 大小,跟开关频率一毛钱关系都没有。

高级功能解锁: 正因为这个引脚的存在,你可以通过控制 SS/TR 引脚的电压,实现多路电源的比率跟踪 或顺序上电 。这对于给 FPGA 的内核电压 (Core) 和 I/O 电压做上电时序控制,是唯一的正解 。

免责声明:本文参考@电源先生 通仅作学习与参考之用。本号对所有原创及转载内容所涉及的陈述与观点均保持中立立场,推送文章仅供读者学习交流。文中涉及的文字、图片等版权均归原作者所有,如存在侵权情况,请及时联系删除。