德思特干货 | 工程师必备:I2C 通信协议全解析!从时序到硬件,一文搞定低速外设通信

背景

在嵌入式系统开发中,低速外设的通信互联是核心需求之一。从传感器数据采集、EEPROM 存储读写,到 OLED 屏显控制,都需要稳定可靠的总线协议支撑。而 I2C(Inter-Integrated Circuit)协议凭借 “仅需两根线” 的极简架构、多主多从的灵活拓扑,以及完善的应答机制,成为低速外设通信的首选方案,广泛应用于消费电子、工业控制、物联网设备等场景。

然而,不少工程师在实际调试中常会遇到时序冲突、上拉电阻选型不当、总线电容超标等问题,影响项目进度。德思特Salland ADC/DAC测试系统支持I2C协议,本文结合实战经验,从基础概念、时序流程、速度选型到硬件落地,全面拆解 I2C 协议核心要点,帮你快速扫清认知盲区,高效解决开发难题。

什么是I2C

I2C(Inter-Integrated Circuit)是一种同步、串行、半双工通信总线协议,用于连接低速外设。

I2C 只有两根必须的线,所有设备都挂在这两根线上(类似 “共享电话线”):

・SCL(Serial Clock):时钟线由「主设备」控制,像 “打节拍”—— 主设备按节奏拉高低电平,所有设备都跟着这个节奏读 / 写数据(确保同步)。

・SDA(Serial Data):数据线主从设备通过这根线传递实际数据(比如传感器的温度值、OLED 的显示指令),但只有 “主设备允许时”,从设备才能拉低这根线。

还有一个隐性规则:主设备说了算(决定和哪个从设备通信、什么时候发数据),从设备只负责 “听指令、回应”。

I2C的物理接口特性

・开漏输出(需上拉电阻)

・多主多从架构

・总线空闲时均为高电平

・低电平有效(0=有效,1=空闲)

I2C波形时序详解

起始条件(S)

1. SCL必须为高电平

2. SDA从高电平变为低电平

停止条件(P)

1. SCL必须为高电平

2. SDA从低电平变为高电平

数据传输位

1. SCL低电平期间:SDA可以改变状态

2. SCL高电平期间:SDA必须保持稳定

3. 数据在SCL上升沿被采样

应答机制(ACK/NACK)

I2C最大的一个特点就是有完善的应答机制,从机接收到主机的数据时,会回复一个应答信号来通知主机表示“我收到了。

1. 每个字节后都有第9个时钟周期

2. 发送方释放SDA(高阻态)

3. 接收方在第9个时钟期间:

・ACK:拉低SDA(确认收到)

・NACK:保持SDA高(错误/结束)

总结

写寄存器的标准流程为:

波形时序:

[START][ADDR:0x50+W][ACK][DATA1][ACK][DATA2][ACK]...[STOP]

1. Master发起START

2. Master发送I2C addr(7bit)和w操作0(1bit),等待ACK

3. Slave发送ACK

4. Master发送reg addr(8bit),等待ACK

5. Slave发送ACK

6. Master发送data(8bit),即要写入寄存器中的数据,等待ACK

7. Slave发送ACK

8. 第6步和第7步可以重复多次,即顺序写多个寄存器

9. Master发起STOP

读寄存器的标准流程为:

波形时序:

[START][ADDR:0x50+R][ACK][DATA1][ACK][DATA2][ACK]...[NACK][STOP]

1. Master发送I2C addr(7bit)和w操作1(1bit),等待ACK

2. Slave发送ACK

3. Master发送reg addr(8bit),等待ACK

4. Slave发送ACK

5. Master发起START

6. Master发送I2C addr(7bit)和r操作1(1bit),等待ACK

7. Slave发送ACK

8. Slave发送data(8bit),即寄存器里的值

9. Master发送ACK

10. 第8步和第9步可以重复多次,即顺序读多个寄存器

I2C协议版本与速度

工作模式对比

选择建议

1. 标准模式(100kHz):大多数传感器、EEPROM

2. 快速模式(400kHz):需要较高速度的外设

3. 高速模式:特殊应用,需要主设备支持

硬件实现注意事项

I2C 采用的 GPIO 一般为开漏模式,支持线与功能,但是开漏模式无法输出高电平,所以需要外部上拉。Vdd 可以采用 5V、3.3V、1.8V等,电源电压不同,上拉电阻阻值也不同。

一般认为 I2C 总线上,低于 0.3Vdd 为低电平,高于 0.7Vdd 为高电平。120 协议中每个挂到总线上的设备都有独一无二的静态设备地址。空闲时,120 总线上两根线都是高电平,因为有上拉电阻。

上拉电阻计算

计算依据:

1. 总线电容(Cb):所有设备引脚电容之和 + 线路电容

2. 上升时间要求:标准模式≤1000ns,快速模式≤300ns

3. 电源电压:通常3.3V或5V

计算公式:

常用值:

・标准模式(100kHz):4.7kΩ - 10kΩ

・快速模式(400kHz):2.2kΩ - 4.7kΩ

・快速模式+(1MHz):1kΩ - 2.2kΩ

实际建议:

总线电容限制

最大总线电容:

・标准模式:400pF

・快速模式:200pF

・快速模式+:100pF

电容计算示例:

每个 I2C 器件引脚:5-10pF

PCB走线:约1pF/cm

连接器:5-20pF

总电容 = Σ器件电容 + 走线电容

解决方案:

1. 减少连接设备数量

2. 缩短走线长度

3. 使用缓冲器(如PCA9515)

附录

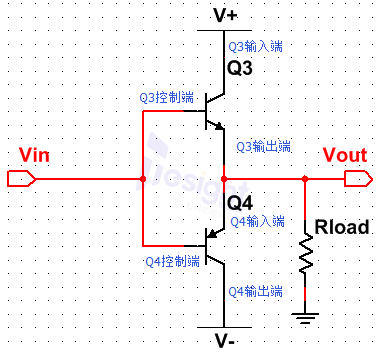

推挽结构

推挽结构是一种输出级设计,它使用两个互补的MOSFET(一个NMOS,一个PMOS)来驱动输出级

核心特点:

1. 驱动能力强:无论是输出高电平还是低电平,都能提供较低的输出阻抗,可以快速对负载电容进行充放电,适合驱动需要高速开关的负载(如LED、MOSFET栅极等)。

2. 定义明确的高低电平:输出要么是 VDD,要么是 GND,没有不确定状态(前提是总线没有冲突)。

3. 不能直接“线与”:如果将两个推挽输出直接连在一起,如果一个要输出高(VDD),另一个要输出低(GND),就会形成一条从 VDD 到 GND 的低阻通路,产生很大的短路电流,可能烧毁芯片。

典型应用:

・GPIO通用输出(当需要强驱动时)

・地址/数据总线

・驱动LED、继电器

・时钟信号(如SPI的SCLK)

・大多数微控制器引脚在配置为“输出”模式时,默认就是推挽模式。

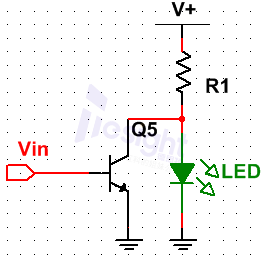

开漏结构

开漏结构与推挽结构的关键区别在于:它只有“下拉”管,没有“上拉”管。开漏输出的N-MOS管的漏极是“开路”的,需要外部连接一个上拉电阻到电源。

核心特点:

1. 电平转换:输出的高电平电压由外部上拉电阻所连接的电源 Vpull-up 决定。这使得开漏输出可以轻松实现电平转换。例如,一个3.3V的MCU可以用5V上拉,输出5V高电平,与5V系统通信。

2. “线与”功能:这是开漏结构最重要的特性之一。多个开漏输出可以直接连在一起,共用同一个上拉电阻。

・只有当所有输出都为高阻态(即逻辑1)时,总线才被上拉为高电平。

・只要任意一个输出导通拉低,总线就是低电平。

・这实现了硬件上的“与”逻辑(负逻辑,低有效),非常适用于总线通信(如I2C)和中断信号线。

3. 驱动能力较弱(上升沿):从低电平变为高电平,完全依靠上拉电阻对总线电容充电,速度较慢。上拉电阻值越小,速度越快,但功耗越大。需要在速度和功耗之间折中。

4. 多主设备仲裁的基础:I2C总线正是利用“线与”特性,允许多个主设备竞争总线而不会损坏硬件。

典型应用:

・I2C、SMBus 等双向通信总线(必须使用开漏)

・多设备共享的中断请求线

・电平转换电路

・驱动高于芯片电压的器件(如用3.3V GPIO控制5V MOSFET)

核心区别总结